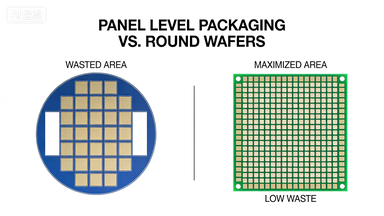

Are rising chip costs hurting your budget? Wasted silicon makes traditional packaging expensive. Panel Level Packaging1 solves this problem. It maximizes space and cuts your production expenses.

Panel Level Packaging1 (PLP) builds chip packages on large square glass panels2 instead of round silicon wafers. This square shape allows manufacturers to use over 90% of the surface area. This method significantly reduces the unit cost of high-performance electronic components.

I remember visiting a massive assembly plant early in my career. I watched machines cut square chips out of round wafers. The machines left so much empty space at the edges. That wasted space always bothered me. Now, the industry finally has a better way to handle this waste. Let me explain how this shift to square panels changes everything.

How does packaging on square glass panels2 change the game?

Do round wafers limit your chip output? Curved edges waste valuable space. They increase your costs. Square glass panels fix this issue. They offer a perfect fit for square chips.

Square glass panels match the shape of the chips perfectly. This design removes the empty edge space found on round wafers. Manufacturers pack more chips onto a single panel. This change increases the total output. It makes the whole process much more efficient.

The Shift from Round to Square

I started working in the electronic components industry over 20 years ago. I spent a lot of time on factory floors. I always saw the same problem. Engineers placed square chips on round silicon wafers. The edges of the round wafers could not hold whole chips. Factories threw away a large amount of good material. This waste cost companies a lot of money.

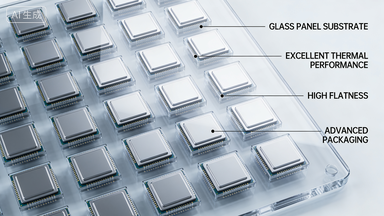

Today, the industry uses square glass panels2. Glass is very flat. Glass is also very strong. These qualities make glass perfect for advanced packaging3. We can fit square chips onto a square panel without wasting the edges. Glass also handles heat better than silicon. Advanced chips generate a lot of heat. The glass panels help keep the chips cool. Hardware engineers love this feature. They can design smaller devices. They do not have to worry about overheating.

Impact on Hardware Production

Hardware engineers need reliable MCUs and sensors. They also need steady production schedules. Square panels allow factories to make more chips at once. This speed helps us deliver parts to you on time. At Nexcir, we always look for these smart manufacturing upgrades. We want to ensure you get high-quality components without delays.

| Feature | Round Silicon Wafer | Square Glass Panel |

|---|---|---|

| Base Shape | Round | Square |

| Edge Waste | High | Very Low |

| Thermal Performance | Good | Excellent |

| Output Volume | Standard | Very High |

This simple change in shape brings massive benefits. I talk to OEM procurement managers4 every day. They worry about supply shortages. The square panel method solves many supply issues. It allows factories to produce more units in the same amount of time. We use this industry knowledge to optimize your supply chain. We help you avoid production stops.

Why does a 90% utilization rate5 matter for high-value chips like HBM?

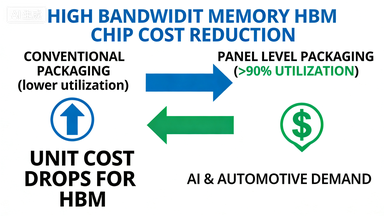

Are high High Bandwidth Memory6 costs stopping your projects? Low wafer use makes these chips too expensive. A 90% utilization rate5 drives these unit costs down fast.

A 90% utilization rate5 means almost no material goes to waste. Manufacturers use more of the panel surface. Therefore, they produce more chips per batch. This high efficiency dramatically lowers the unit cost for expensive components like High Bandwidth Memory6.

Lowering Costs for Advanced Technology

High Bandwidth Memory6 (HBM) is very important today. AI servers need HBM to work fast. Many automotive systems also use HBM. But HBM is very expensive to make. Data centers buy thousands of AI servers. Each server needs many HBM chips. The demand for HBM is growing very fast. Traditional factories cannot keep up with this demand. They waste too much time and material. Panel Level Packaging1 solves this supply problem.

I often hear from production teams. They complain about the high price of these memory chips. Traditional round wafers only use about 85% of their surface. The factory loses the other 15%. This loss makes each chip more expensive. Panel Level Packaging1 changes this math. The square glass panels2 push the utilization rate above 90%. Sometimes factories reach 95% utilization. This high rate drops the unit cost significantly. Procurement managers need to lower their costs. They want to improve their overall competitiveness. This new packaging method helps them reach their goals.

Securing Stable Pricing

I always want to get the best prices for my customers. We have long-term partnerships with global suppliers. We understand how new manufacturing methods affect market prices. We use this information to secure stable pricing for you.

| Cost Factor | Traditional Wafer Method | Panel Level Packaging1 |

|---|---|---|

| Surface Utilization | ~85% | >90% |

| Unit Cost | Very High | Much Lower |

| Production Efficiency | Moderate | Excellent |

| Market Price Stability | Volatile | More Stable |

We protect you from market fluctuations. We ensure you get 100% original electronic components at a fair price. You can trust us to manage your procurement risks. We will always find the best supply solutions for your business.

Will foundries like TSMC unify PLP standards by 2026?

Does the lack of clear rules confuse your supply chain? Different factory setups cause delays. Unified standards from top foundries will bring order and speed very soon.

Major foundries like TSMC are working hard. They want to create unified rules for Panel Level Packaging1 by 2026. These shared standards will make equipment and materials work together smoothly. This unification will help the whole industry produce components faster.

The Road to Unified Standards

The electronics industry needs rules to work well. Right now, different factories use different panel sizes. Some factories use 510mm by 515mm panels. Other factories use 600mm by 600mm panels. This difference creates a big problem. Equipment makers cannot build standard machines. Material suppliers cannot make standard glass. This confusion causes delays in the supply chain. I have seen this happen many times in my 20 years of experience.

Top foundries understand this problem. TSMC is leading the way to fix it. They plan to establish standard panel sizes7 by 2026. They will also set rules for the manufacturing process. This unification is great news for everyone. Counterfeit products are a big worry in our industry. Standardized processes make it harder for bad actors to fake chips. Every step of the process becomes traceable. We only buy from authorized distributors. We guarantee 100% authentic components. Standardized PLP will make our traceability8 even stronger.

Building a Reliable Future

Standard rules mean faster production. Faster production means stable lead times for you. Hardware engineers will find it easier to source parts. Procurement teams will face fewer delays.

| Industry Aspect | Current State (Pre-2026) | Future State (Post-2026) |

|---|---|---|

| Panel Sizes | Many different sizes | One or two standard sizes |

| Equipment | Custom and expensive | Standard and cheaper |

| Lead Times | Unstable | Highly predictable |

| Traceability | Good | Excellent |

At Nexcir, we closely watch these industry trends. We prepare our global supply network9 for these changes. We want to be your trusted long-term partner. We will help you navigate this transition. We will ensure your production schedule remains stable. We will always provide professional support for your supply chain.

Conclusion

Panel Level Packaging1 uses square panels to cut waste. This method lowers costs for advanced chips. Unified standards will soon make this process better. We will guide you through it.

Panel Level Packaging is a revolutionary method that reduces production costs by maximizing space utilization, making it essential for cost-effective manufacturing. ↩

Square glass panels eliminate edge waste and improve thermal performance, making them a superior choice for efficient chip packaging. ↩

Advanced packaging with square glass panels offers better space utilization and thermal management, crucial for high-performance electronic components. ↩

Panel Level Packaging helps OEM procurement managers lower costs and improve competitiveness by optimizing supply chains and reducing waste. ↩

Achieving a 90% utilization rate minimizes material waste, significantly lowering the cost of high-value chips like High Bandwidth Memory. ↩

Panel Level Packaging increases surface utilization, reducing the unit cost of High Bandwidth Memory, crucial for AI servers and automotive systems. ↩

Standard panel sizes will eliminate confusion, allowing for more efficient equipment manufacturing and material supply, speeding up production. ↩

Standardized PLP enhances traceability, making it harder for counterfeit products to enter the market, ensuring authenticity and quality. ↩

Nexcir is adapting its global supply network to embrace PLP changes, ensuring stable production schedules and professional support for clients. ↩