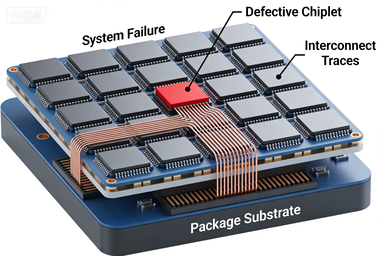

High chip manufacturing costs hurt your budget. You switch to chiplets to save money. But your total expenses still rise. The hidden problem is the yield trap1.

The yield trap1 of chiplets happens when one defective small chip ruins the entire packaged system. While making small chips costs less, testing them to ensure they are Known Good Dies (KGD)2 before packaging makes the final production costs much higher than expected.

I faced this exact problem last year. A client wanted to lower costs with chiplets. They thought it was a magic fix. But hidden packaging failures ate up all their savings. You need to understand this trap before you plan your next procurement project. Let us look closer at how this happens. I will explain the core logic first. Then I will show you the main business pain point. Finally, I will share my observation for the year 2026. This knowledge will help you reduce procurement risks. It will also help you ensure product authenticity and stable pricing.

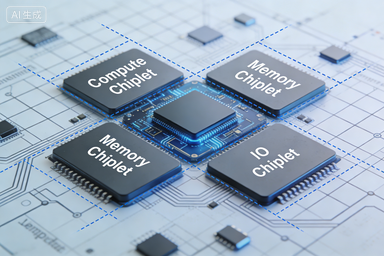

Why Do We Split Large Chips into Smaller Chiplets?

Large chips have high defect rates. One flaw ruins the whole expensive piece. By splitting them into smaller parts, you get better yields. You also save money on basic manufacturing.

We split large chips into smaller chiplets to improve manufacturing yields. Smaller chips have fewer defects per wafer. You can mix different parts like memory and logic. This modular approach3 reduces waste. It also speeds up the design process for complex electronic systems.

Let us break down the core logic of chiplets. Hardware engineers design huge systems on a chip. We call this a SoC. They face a big problem during production. A large silicon area means a higher chance of hitting a microscopic defect. A single defect ruins a huge chip. You must throw the whole thing away. This is a nightmare for procurement managers. You need stable pricing. You need low costs. You cannot afford high waste.

The Modular Advantage

Instead of one big block, we make several small blocks. We call these small blocks chiplets. You can build these small chiplets using different technology nodes4. For example, you can use an expensive 3nm process for the main core processor. Then, you can use a cheaper 14nm process for the basic input and output parts. This method saves a lot of money. Our core team at Nexcir5 has over 20 years of experience. We always help clients find these cost-effective matches. We want to lower your procurement costs. We want to enhance your overall competitiveness.

Cost Comparison Table

| Feature | Traditional Large Chip | Chiplet Design |

|---|---|---|

| Manufacturing Yield | Low because of large area | High because of small area |

| Technology Node | Same for all parts | Mixed nodes save money |

| Design Flexibility | Hard to change later | Easy to upgrade parts |

| Material Waste | Very high | Very low |

This modular method looks perfect on paper. It helps factories avoid the high costs of advanced nodes. It gives you flexible service models. But this is only the first step of the journey. The real challenge hides in the next step. The packaging stage6 brings a new set of problems.

Why Do KGD Testing Costs Soar in the Packaging Stage?

You saved money making small chips. But now you must pack them together. If one bad chiplet gets inside, the whole package dies. This wastes all your money.

Testing costs soar because you must ensure every small chip is a Known Good Die (KGD) before packaging. If one defective chiplet is packaged with good ones, the entire expensive system fails. Advanced testing methods take more time, need special equipment, and greatly increase your total production budget.

![]()

The true pain point for hardware engineers hits during the packaging stage6. I remember a project very clearly. A client skipped strict KGD testing to save time. They packed four good chiplets and one bad chiplet together. The result was terrible. They had to throw away the whole system. One bad apple ruined the whole basket. This destroyed their production schedule.

The High Price of Certainty

Factories must test every single chiplet very carefully to stop this waste. We call this finding the Known Good Die. We also call it KGD. Testing naked, unpackaged dies is very hard. The contact pads are tiny. Standard testing probes can damage them easily. You need expensive, high-precision tools7. This testing slows down the production schedule. As a buyer, you hate delays. You expect on-time delivery. You want to maintain production schedule stability8.

Testing Impact on Procurement

| Cost Factor | Standard Single Chip | Chiplet Package System |

|---|---|---|

| Testing Phase | After final packaging | Before and after packaging |

| Equipment Cost | Normal standard tools | Very high precision probes |

| Scrap Cost Risk | Low for single die | Very high for multi-die |

| Lead Time | Easy to predict | Often faces long delays |

The money you saved in the silicon factory is now lost in the testing house. You want stable pricing without market fluctuations. But KGD testing makes costs unpredictable. We at Nexcir5 work hard to solve this. We source fully verified, original components. We guarantee authentic components9. We ensure full traceability10 for every shipment. This helps you avoid these surprise costs.

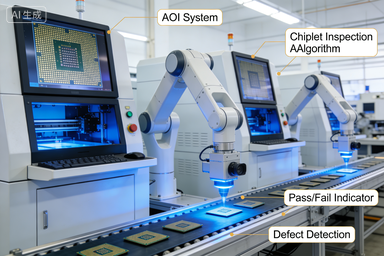

How Will OSATs Use AOI to Reduce Scrap Rates by 2026?

High scrap rates11 destroy your profit margins. Manual checks miss tiny flaws on complex chiplets. Automated Optical Inspection will fix this by catching bad chips early in the process.

By 2026, Outsourced Semiconductor Assembly and Test companies will use advanced Automated Optical Inspection to find defects. This technology uses high-resolution cameras and artificial intelligence12 to spot micro-cracks on chiplets. This stops bad chips from entering the package, reducing scrap rates11 and lowering final costs.

Looking ahead to the year 2026, the supply chain must solve this yield trap1. Outsourced Semiconductor Assembly and Test companies are spending a lot of money on new tools. We call these companies OSATs. The biggest game-changer is Automated Optical Inspection. We call this AOI. As a distributor with global supply networks13, I see this shift happening right now.

The Power of Automated Vision

AOI machines use powerful lenses and smart software. They scan the surface of every chiplet before packaging. They look for tiny cracks. They look for bad solder bumps. They look for microscopic dirt. A human eye cannot see these flaws. Even older machines miss them. By catching the bad apples early, OSATs ensure only perfect KGDs go into the final package. This keeps your production schedule stable. It ensures on-time delivery.

AOI Benefits for the Supply Chain

| Metric | Without Advanced AOI | With 2026 AOI Technology |

|---|---|---|

| Defect Detection | Low rate of success | Very high with smart AI |

| System Scrap Rate | High when one die fails | Low because bad dies go away |

| Overall Cost | Unpredictable and high | Stable and much lower |

| Trust in Supply | Low confidence | High confidence and trust |

When OSATs lower their scrap rates11, your procurement costs drop. This directly solves the pain point of high prices. At Nexcir5, we always track these technology trends. We collaborate with trusted global logistics partners. We make sure our network partners with the most advanced factories. This guarantees you get authentic parts. We operate with transparency and integrity. We ensure you have full visibility throughout the entire procurement process.

Conclusion

Chiplets save manufacturing costs but create a testing yield trap1. By understanding KGD challenges and upcoming AOI technologies, you can optimize procurement and ensure stable electronic component supply.

Understanding the yield trap is crucial for avoiding unexpected costs in chiplet production, ensuring better budget management. ↩

KGD testing ensures only defect-free chiplets are used, preventing costly failures in the final product. ↩

Exploring the modular approach reveals how it enhances flexibility and reduces waste in chiplet manufacturing. ↩

Understanding technology nodes helps in selecting cost-effective processes for different chiplet components. ↩

Nexcir provides expertise in sourcing cost-effective chiplet solutions, enhancing competitiveness in the market. ↩

The packaging stage can introduce defects, making it essential to understand its impact on overall production costs. ↩

High-precision tools are vital for accurate KGD testing, preventing damage to chiplets and ensuring quality. ↩

Maintaining production schedule stability ensures timely delivery and cost predictability in chiplet manufacturing. ↩

Authentic components ensure reliability and quality, preventing costly failures in electronic systems. ↩

Traceability guarantees authenticity and quality, reducing risks in the procurement process. ↩

High scrap rates lead to increased costs, making it essential to explore methods to reduce them. ↩

AI enhances defect detection in chiplets, ensuring only high-quality components are packaged. ↩

Global supply networks ensure access to advanced technologies and authentic components, stabilizing costs. ↩